Table of Contents

Documentation & How-to

Here you will find documentation and how-to about the environment used by CorteXlab and provided to users.

CorteXlab

Experimental workflow

The process of running experiments on the FIT/CorteXlab testbed involves several steps:

- Developing an experiment

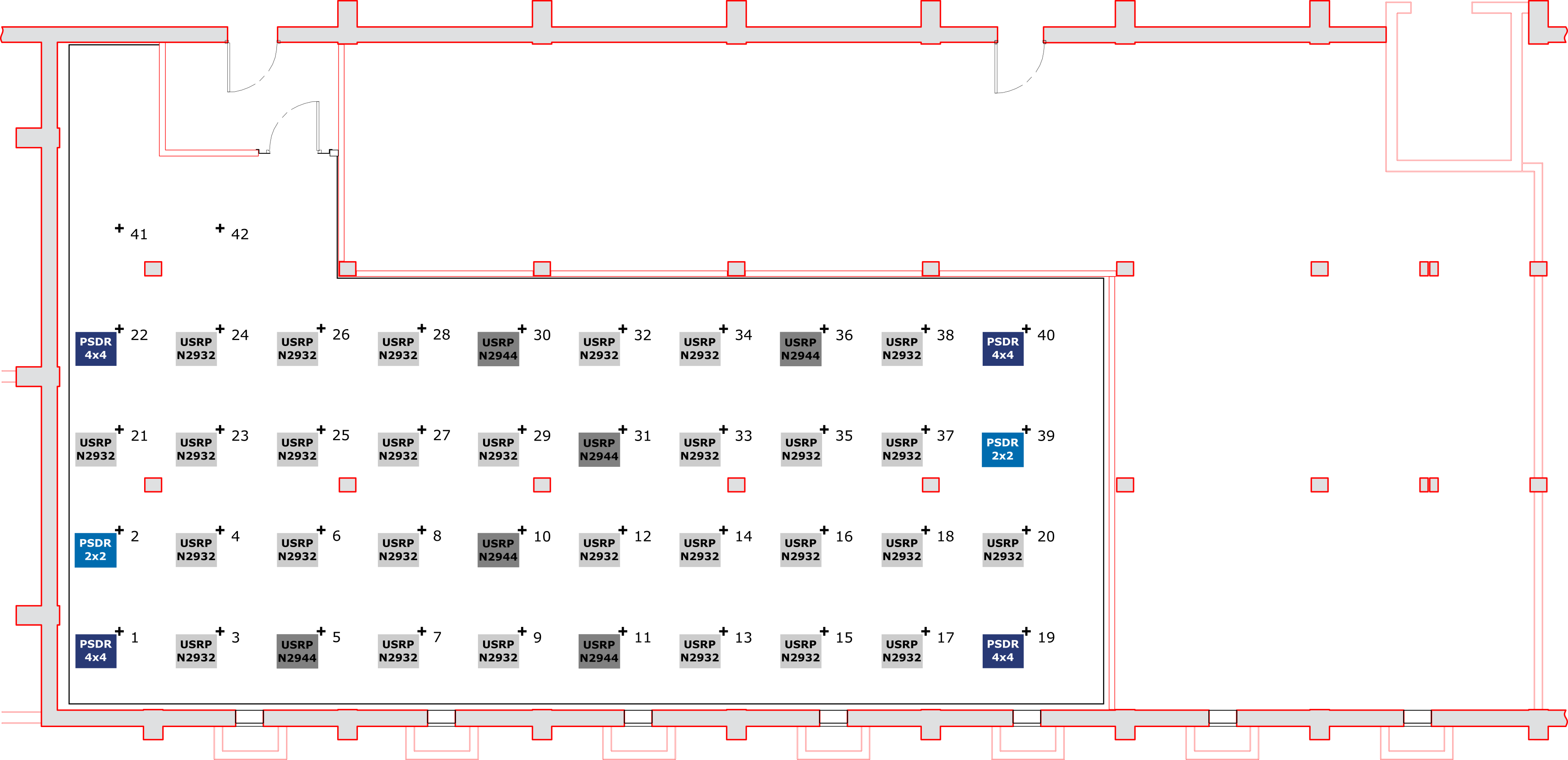

Node position map

Minus

GNURadio

- Building a toolchain How to install the toolchain (including GNURadio) used within CorteXlab on your computer in order to have the same development environment

- Embedding OOT modules or custom libraries/binaries in a minus scenario How to have a self-explanatory link

- FFT Web Documentation about FFT Web GNURadio block

USRPs

There 34 USRPs installed in the FIT/CorteXlab room.

- 28 are of type NI-2932 (equivalent USRP N210 with a SBX daughterboard). Here are the main characteristics of these (for more details refer to the USRP-2932 specifications page at NI):

- Frequency range: 400 MHz to 4.4 GHz

- One Gigabit/s ethernet attachment to control node

- Maximum bandwidth: 20 MHz (but in practice less than 20 MHz are usable without loss of samples due to either the gigabit ethernet connectivity or the computing power of the signal processing computer)

- Full-duplex TX and RX chains. There are antennas connected to the

TX/RXandRX2ports of all USRPs. In the case theTX/RXports are used, then only half-duplex is supported - Synchronization: All USRPs are connected to a stack of octoclocks (see below for more info) and can be configured to work in synchronized mode by selecting

external clock sourcein the USRP sink or source configuration.

- 6 are of type N2944R (equivalent of X310). Here are the main characteristics of these (for more details refer to the USRP-2944 specifications page at NI):

- Frequency range: 10 MHz to 6 GHz

- Dual 10 Gigabit/s ethernet attachment to control node

- Maximum bandwidth: 160 MHz (theorically, the dual 10 Gigabit/s ethernet attachment should be sufficient to transfer this whole bandwidth, but in practice in most cases the computing power of the signal processing computer will limit that)

- Synchronization: All USRPs are connected to a stack of octoclocks (see below for more info) and can be configured to work in synchronized mode by selecting

external clock sourcein the USRP sink or source configuration.

Find here tutorials on how to use them

Antennas

Every SDR inside the experimentation room uses the Aaronia OmniLOG® 70600 Wideband antenna, spanning 680 MHz – 6 GHz with gains ranging between -15 dBi and +2 dBi.

Every antenna is mounted on the ceiling of the experimentation room at the positions indicated by the “+” mark on the room layout picture above. The antennas are mounted upside down with its horizontal plane parallel to the plane of the room.

In the case of the USRPs NI 2932, both the TX/RX and RX2 connectors have an antenna connected to them, ads well as all antenna connectors for the NI 2944R.

Here's the horizontal radiation pattern and gain diagrams for your convenience (taken from the antennas datasheet):

More info can be found in its datasheet

Octoclocks

A hierarchy of octoclocks allow the reference and timing distribution to all USRPs in CorteXlab. All cables are of same length (5m between master and slave octoclocks and 10m between slave octoclocks and USRPs). The connection layout is as shown below. The octoclock 0 is the master and the octoclocks 1-4 are the slave ones.

Timing measurements in the CorteXlab room:

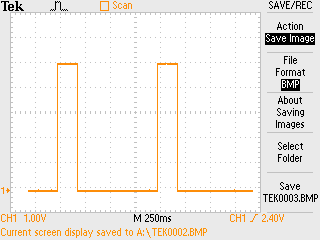

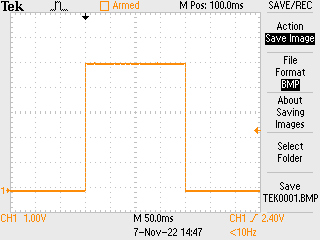

The octoclock produces a PPS signal that has a period of 1s and remains high during 200ms and low 800ms as shown below:

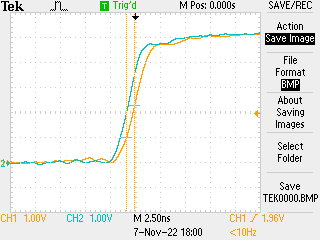

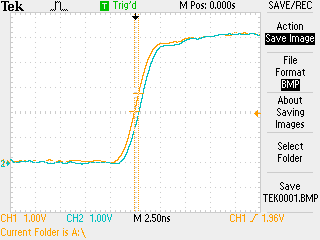

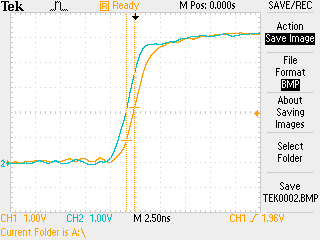

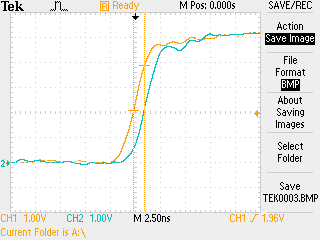

The PPS signals between the slave octoclocks in the room are mismatched by a maximum of 800ps as shown below (examples):

Between nodes 28 (connected to octoclock 3) and 31 (connected to octoclock 4)

Between nodes 31 (connected to octoclock 4) and 14 (connected to octoclock 2)

Between nodes 14 (connected to octoclock 2) and 10 (connected to octoclock 1)

Between nodes 10 (connected to octoclock 1) and 27 (connected to octoclock 3)

For more (updated) info on the octoclocks: